100G LR1 SFP56-DD光トランシーバ(100G SFP56-DD LR1)は、シングルモード光ファイバ(SMF)による最大10kmの100ギガビットイーサネットリンクでの使用向けに設計されています。SFP56-DD MSA、IEEE802.3CU、100G Lambda 100G LR1、および100GAUI-2(FECなし)1に準拠しています。SFP56-DD MSAで規定されているI2Cインターフェースを介して、デジタル診断機能も利用できます。

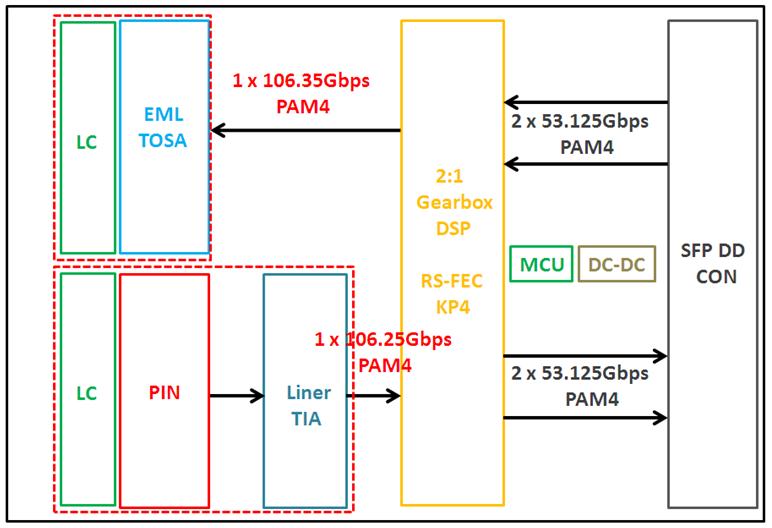

このモジュールは、中心波長1311nmの1チャネル光信号を内蔵し、100Gbpsのデータレートで動作します。このモジュールは、2チャネルの53Gbps(PAM4)電気入力データを1チャネルの106Gbps(PAM4)光信号に変換し、また1チャネルの106Gbps(PAM4)光信号を2チャネルの53Gbps(PAM)電気出力データに変換できます。光インターフェースにはデュプレックスLCコネクタを採用しています。高性能冷却EMLトランスミッタと高感度PINレシーバは、最大10kmリンクの100ギガビットイーサネットアプリケーションにおいて優れた性能を発揮します。

100G LR1 10km SFP-DD光トランシーバー RSD-100G-LR1

特徴

アプリケーション

注記:

1. KR-FECはオプションですので、必要な場合はお問い合わせください。

図1. モジュールブロック図

絶対最大定格

| パラメータ | シンボル | 分 | マックス | ユニット |

| 供給電圧 | Vcc | -0.3 | V | |

| 入力電圧 | ヴィン | -0.3 | Vcc+0.3 | V |

| 保管温度 | Ts | -20 | 85 | ℃ |

| ケース動作温度 | TC | 0 | 70 | ℃ |

| 湿度(結露なし) | ロジウム | 5 | 85 | % |

推奨動作条件

| パラメータ | シンボル | 分 | 典型的な | マックス | ユニット |

| 供給電圧 | Vcc | 3.13 | 3.3 | 3.47 | V |

| 動作ケース温度 | TC | 0 | 70 | ℃ | |

| レーンあたりのデータレート | fd | 106.25 | ギガビット/秒 | ||

| 湿度 | ロジウム | 5 | 85 | % | |

| 消費電力 | 午後 | 3 | 3.5 | W | |

| G.652 によるリンク距離 | D | 10 | キロ |

電気仕様

| パラメータ | シンボル | 分 | 典型的な | マックス | ユニット |

| 差動入力インピーダンス | ジン | 90 | 100 | 110 | オーム |

| 差動出力インピーダンス | ゾウト | 90 | 100 | 110 | オーム |

| 差動入力電圧振幅1 | ΔVin | 1600 | mVp-p | ||

| 差動出力電圧振幅2 | ΔVout | 900 | mVp-p |

注記:

1. 差動入力電圧振幅は、TxnP と TxnN 間で測定されます。

2. 差動出力電圧振幅は、RxnP と RxnN 間で測定されます。

光学特性

| パラメータ | シンボル | 分 | 典型的な | マックス | ユニット | 注記 |

| 送信機 | ||||||

| 中心波長 | λc | 1304.5 | 1317.5 | ナノメートル | ||

| サイドモード抑制比 | SMSR | 30 | dB | |||

| 平均発射パワー | ふくれっ面 | -1.4 | 4.5 | dBm | ||

| 送信機と分散アイ閉鎖(TDECQ) | TDECQ | 3.4 | dB | |||

| 消光比 | 救急外来 | 3.5 | dB | |||

| OFF送信機の平均発射電力 | -30 | dB | ||||

| 受信機 | ||||||

| 中心波長 | λc | 1304.5 | 1317.5 | ナノメートル | ||

| OMA外側の受信感度 | RXsen | -6.1 | dBm | 1 | ||

| 平均受信電力 | ピン | -7.7 | 4.5 | dBm | ||

| 受信機の反射率 | -26 | dB | ||||

| LOSアサート | -13 | dBm | ||||

| LOS アサート解除 – OMA | -11 | dBm | ||||

| LOSヒステリシス | 0.5 | dB | ||||

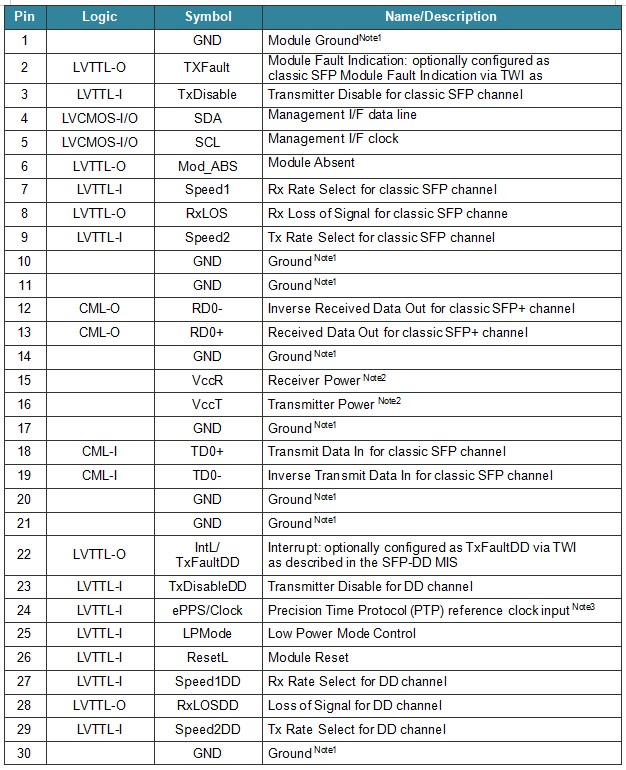

ピンの説明

注記:

1. SFP-DDは、すべての信号と電源に共通グランド(GND)を使用します。SFP-DDモジュール内ではすべて共通であり、特に明記されていない限り、すべてのモジュール電圧はこの電位を基準としています。これらをホストボードの信号共通グランドプレーンに直接接続してください。

2. VccRとVccTは同時に印加され、VccR1とVccT1は同時に印加されるものとします。ホスト側の要件が定義されています。コネクタのVccピンはそれぞれ最大1000mAの電流定格を備えています。

3. ePPS ピン (使用されていない場合) は、ホスト上で 50 Ω でグランドに終端することができます。

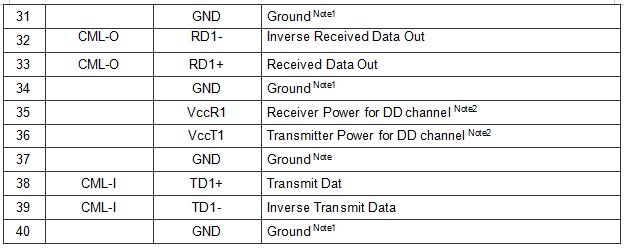

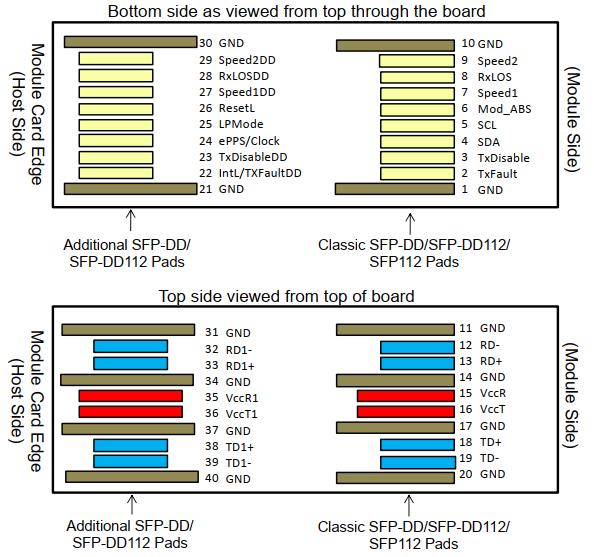

図2. 電気ピン配置の詳細

スピード1、スピード2、スピード1DD、スピード2DD

Speed1、Speed2、Speed1DD、およびSpeed2DDはモジュール入力であり、モジュール内の30kΩ以上の抵抗によってGNDにプルダウンされます。Speed1は、チャネル1の光受信信号レートを任意に選択します。Speed1DDは、チャネル2の光受信信号レートを任意に選択します。Speed2は、チャネル1の光送信信号レートを任意に選択します。Speed2DDは、チャネル2の光送信信号レートを任意に選択します。

注: 128 GFC では、FC LSN は Speed1、Speed2、Speed1DD、および Speed2DD を使用する必要がなくなったため、これらの信号をプログラム可能な機能やその他の機能に再利用することが検討されています。

リセットLピン

リセット。LPMode_Reset はモジュール内に内部プルアップを備えています。ResetL ピンが最小パルス長 (t_Reset_init) より長く低レベルになると、モジュールが完全にリセットされ、すべてのユーザーモジュール設定がデフォルト状態に戻ります。モジュールリセットアサート時間 (t_init) は、ResetL ピンの低レベルが解除された後の立ち上がりエッジから開始されます。リセット (t_init) の実行中、モジュールがリセット割り込みの完了を示すまで、ホストはすべてのステータスビットを無視します。モジュールは、Data_Not_Ready ビットをネゲートした IntL 信号をポストすることで、この完了を示します。電源投入時 (ホットインサーションを含む) には、モジュールはリセットを必要とせずに、このリセット完了割り込みをポストすることに注意してください。

モッド_ABS

Mod_ABSは、ホストボード上でVcc Hostにプルアップし、モジュール内ではLowにプルアップする必要があります。モジュールが挿入されると、Mod_ABSは「Low」にアサートされます。モジュールがホストコネクタから物理的に取り外されると、ホストボード上のプルアップ抵抗により、Mod_ABSは「High」にデアサートされます。

LPモード

LPModeは、アクティブハイロジックで動作するホストからの入力信号です。SFP-DD/SFP-DD112モジュールでは、LPMode信号はVccにプルアップする必要があります。LPMode信号により、ホストはSFP-DD管理仕様で定義されているように、ソフトウェアによって高電力モードへの移行が有効になるまで、SFP-DD/SFP-DD112モジュールを低電力モードのままにするかどうかを定義できます。低電力モード(LPModeがLowにアサート解除されている)では、管理インターフェースの初期化後、モジュールは直ちに高電力モードに移行できます。

リセットL

ResetL信号はモジュール内でVccにプルダウンされます。ResetL信号が最小パルス長(t_Reset_init)よりも長くローレベルになると、モジュールが完全にリセットされ、すべてのユーザーモジュール設定がデフォルト状態に戻ります。

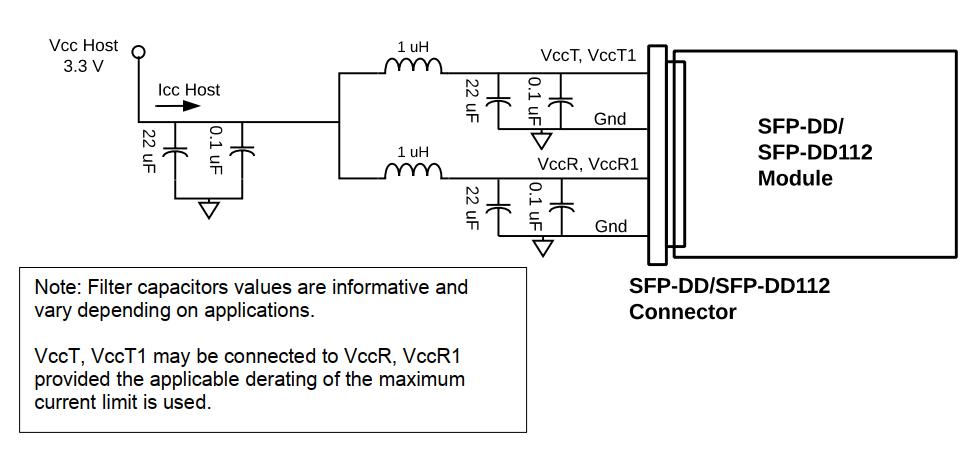

電源フィルタリング

ホスト ボードでは、図 3 に示す電源フィルタリングを使用する必要があります。

図3. ホストボードの電源フィルタリング

診断モニタリングインターフェース(オプション)

以下のデジタル診断特性は、特に指定がない限り、通常の動作条件に基づいて定義されます。

| パラメータ | シンボル | 分 | マックス | ユニット | 注記 |

| 温度モニターの絶対誤差 | DMI_温度 | -3 | +3 | 摂氏度 | 動作温度範囲以上 |

| 供給電圧モニターの絶対誤差 | DMI _VCC | -0.1 | 0.1 | V | 全動作範囲にわたって |

| チャネルRX電力モニターの絶対誤差 | DMI_RX_Ch | -2 | 2 | dB | 1 |

| チャネルバイアス電流モニター | DMI_Ibias_Ch | -10% | 10% | ミリアンペア | |

| チャネルTX電力モニターの絶対誤差 | DMI_TX_Ch | -2 | 2 | dB | 1 |

注:

1. シングルモード ファイバーの測定精度によって、+/- 1 dB の変動がさらに発生したり、合計精度が +/- 3 dB になる場合があります。

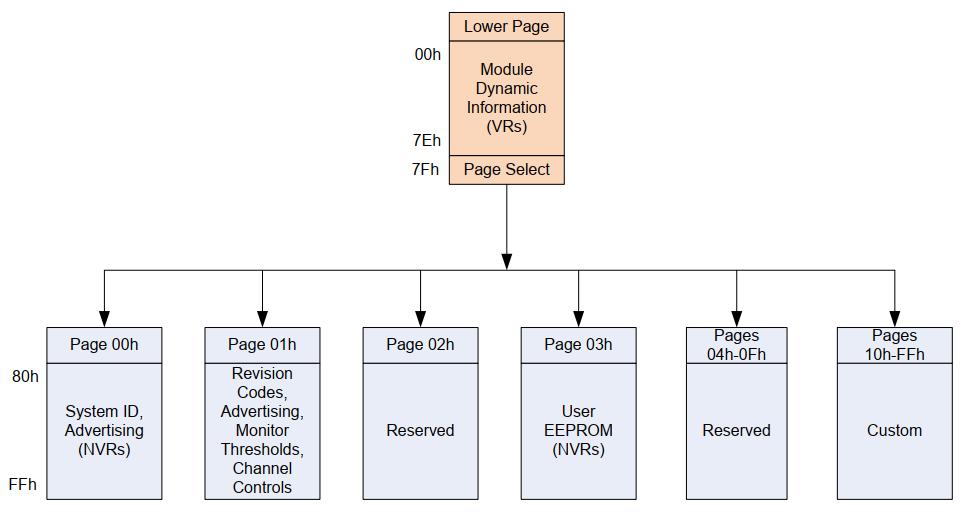

デジタル診断機能は、SFP-DD MISで規定されているI2Cインターフェースを介して利用できます。SFP-DD MIS管理メモリを図4に示します。

8 ビット アドレスのため、ホストが直接アクセスできる管理メモリは 256 バイトに制限され、下位メモリ (アドレス 00h ~ 7Fh) と上位メモリ (アドレス 80h ~ FFh) に分割されます。

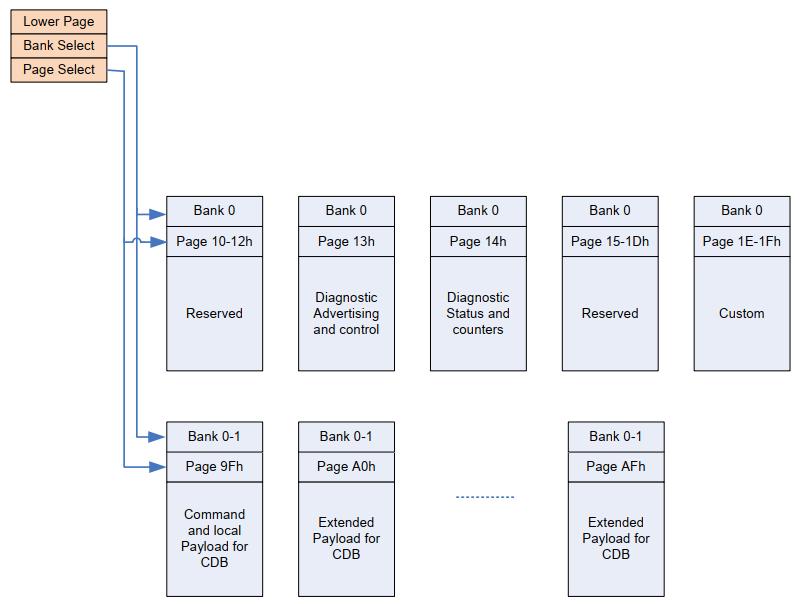

追加の内部管理メモリ1のアドレス構造を図5に示す。

モジュール内の管理メモリは、128バイトの一意かつ常にホストアクセス可能なアドレス空間(下位メモリ)と、それぞれ128バイトの複数の上位アドレス空間(ページ)で構成されており、上位メモリではそのうちの1つだけがホストとして表示されます。複数のインスタンスが存在するページ(例えば、同じページ番号を持つページバンクが存在する場合)については、第2レベルのページ選択が可能です。

この構造は、パッシブ銅線モジュール用のフラットな256バイトメモリをサポートし、フラグやモニターなどの下位メモリ内のアドレスへのタイムリーなアクセスを可能にします。シリアルID情報やしきい値設定など、タイムクリティカルではないエントリは、下位ページのページ選択機能を使用してアクセスできます。より複雑なモジュールで、大量の管理メモリを必要とする場合、ホストは必要に応じて、各ページをホストがアドレス指定可能な上位メモリアドレス空間に動的にマッピングする必要があります。

注:管理メモリマップは、主にCMISメモリマップをモデルに設計されています。CMISメモリマップでは、ページとバンクを使用することで、ホストとモジュール間のタイムクリティカルなやり取りを可能にしながらメモリサイズを拡張しています。このメモリマップは、2つの電気レーンのみに対応し、必要なメモリ容量を制限するために変更されています。QSFPと同様のシングルアドレス方式が採用されています。

図4. QSFP28メモリマップ

図5. SFP-DD MISバンクページメモリマップ

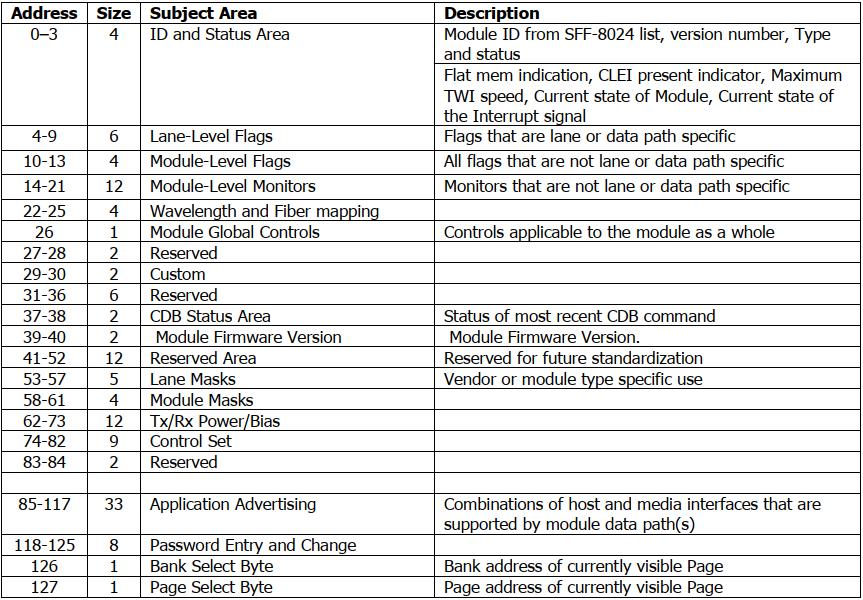

図6. 下部メモリの概要

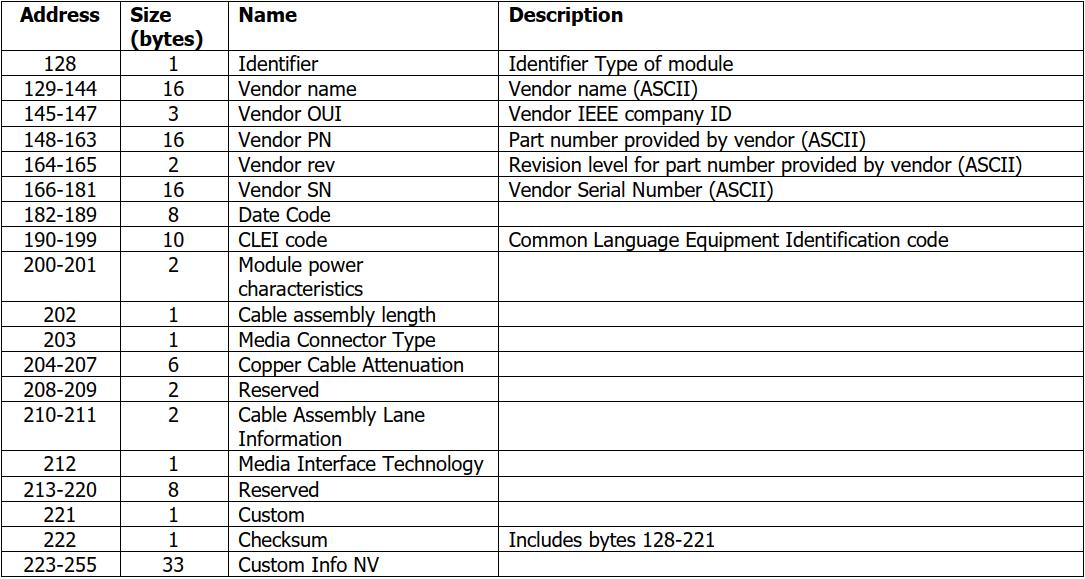

図7. ページ00hのメモリ概要

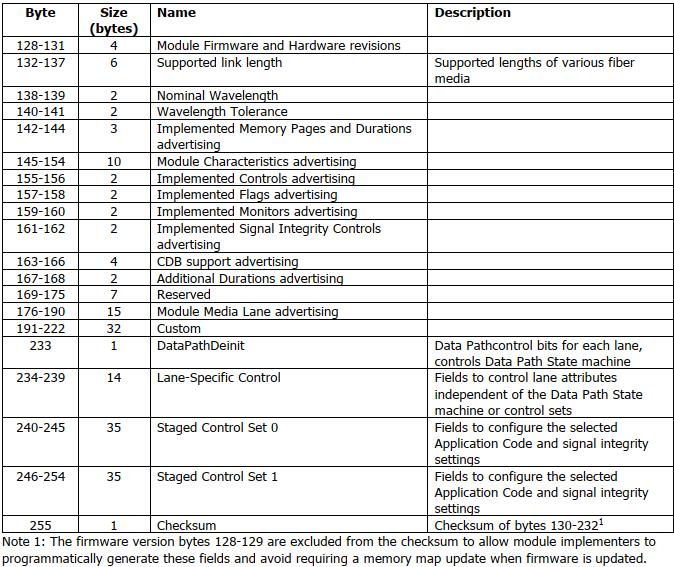

図8. ページ01hのメモリの概要

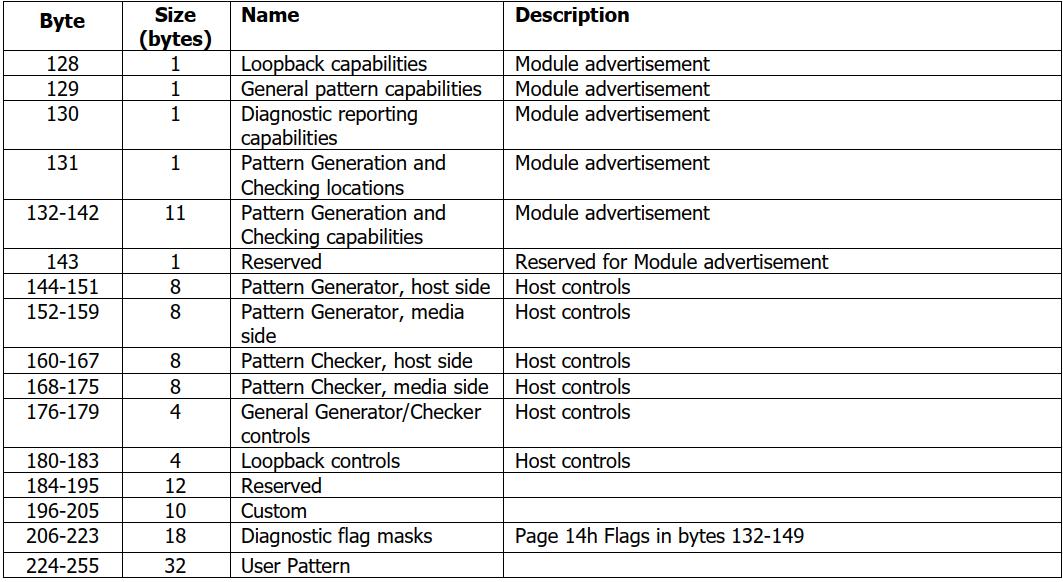

図9. ページ13h メモリの概要

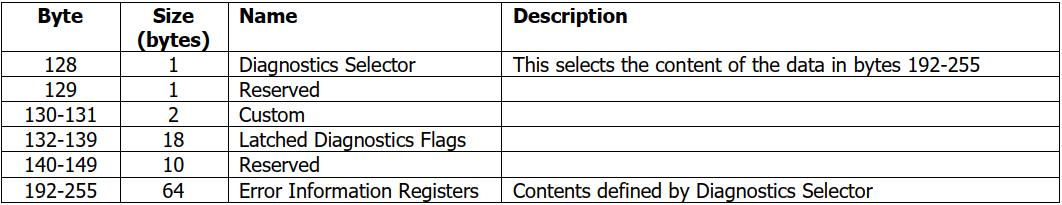

図10. ページ14h メモリの概要

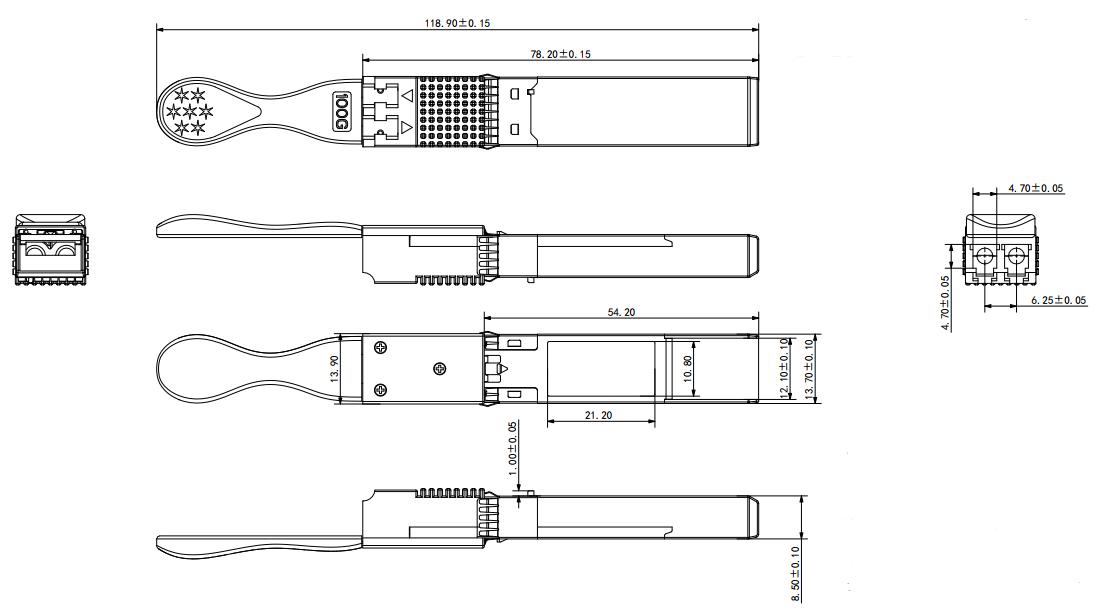

機械寸法

図11. 機械仕様

参考文献

1. SFP-DD MSA

2. IEEE802.3cu 100GBASE-LR1

3. 100G ラムダ MSA 100G LR1-10

注文情報

| 部品番号 | 製品説明 |

| RSD-100G-LR1 | SFP56-DD LR1、106.25Gb/s、10km、EML+PIN、SMF、デュアルLC |

この製品について知りたいですか?

あなたは私達のプロダクトに興味があり、詳細を知りたいのですが、ここにメッセージを残してください